Copyright © 2023 Nanjing Senasic Electronic Technology Co.,Ltd.

**SNP739D0X**

**Highly integrated tire pressure monitoring sensor**

# **SNP739D0X Datasheet**

Release version: Version 2.4

Release date: 2023-12-05

Confidential

**Copyright © 2023 Nanjing Senasic Electronic Technology Co.,Ltd. All rights reserved.**

No part of this document shall be excerpted, translated, reproduced, transmitted, or disseminated by any organization, company, or individual in any form or by any means without the prior written consent of Nanjing Senasic Electronic Technology Co.,Ltd.

### **Consultation Information**

For further information on technical support, delivery and prices, please call the national consultation hotline: **021-5061-0206**, or you can obtain relevant support by email [info@senasic.com](mailto:info@senasic.com).

### **Important Notice**

SENASIC and other SENASIC icons are trademarks of Nanjing Senasic Electronic Technology Co.,Ltd. (former Ningbo SENASIC Electronic Technology Co., Ltd. abbreviated as SENASIC).

The purchased products, services and features are stipulated by the contract made between SENASIC and the customer. All or part of the products, services and features described in this document may not be within the purchase scope or the usage scope. Unless otherwise specified in the contract, all statements, information, and recommendations in this document are provided "AS IS" without warranties, guarantees or representations of any kind, either express or implied.

The content of this document may be changed due to product version upgrades, adjustments, or other reasons. Unless otherwise agreed, this document is used as Use guide only, all statements, information, and recommendations in this document do not constitute a warranty of any kind, express or implied.

Confidential

## Feature

- Calibrated pressure sensor for absolute pressure measurement with optional measurement range:900kPa

- Temperature and supply voltage sensors

- XZ-axis accelerometer with calibration

- 12-bit analog-to-digital converter (ADC12) with two external I/O inputs

- **RF Transmitter**

- On chip PA

- 315/433MHz supported

- Support ASK/FSK modulation

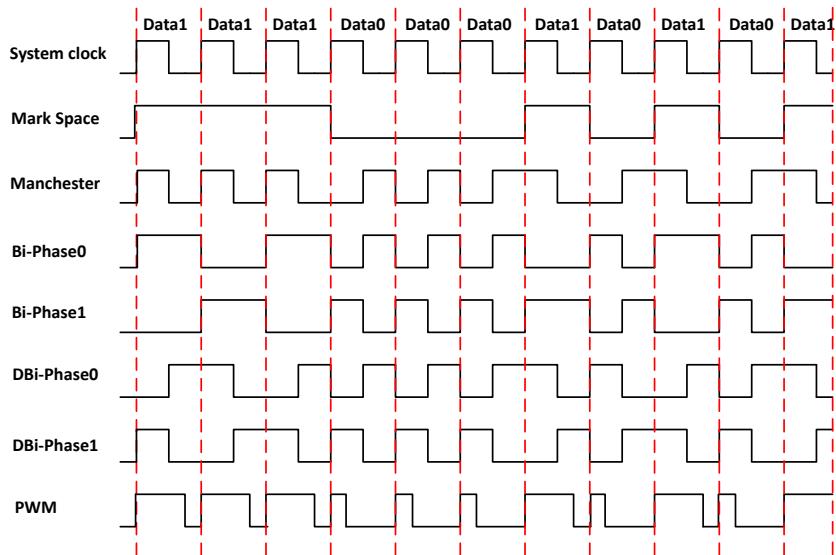

- Support Manchester/PWM/Bi-Phase/Mark-space encoding

- **LF Receiver**

- Support LF programming

- 3.9kbps/6.5kbps supported

- Manchester/PWM encoding

- Carrier or telegram wakeup supported

- Support Wheel Auto Mapping (WAM)

- **On chip RC oscillator**

- 4kHz/39kHz/2MHz

- **MCU**

- 8-bit MCU

- Based on 1T 8051 core

- 16K Bytes Flash

- 32K Bytes ROM

- 256 Bytes data RAM and 128 Bytes retention RAM

- 6 GPIOs, All GPIOs support low power wakeup

- SPI/UART/I2C/LIN interface supported

- Timer 8 with PWM function

- Standby current 0.2μA

- Package: LGA 24pins. 6.0mmx5.0mmx1.9mm

## Applications

- Tire Pressure Monitoring sensor

- MEMS sensing

## Contents

|          |                                        |           |

|----------|----------------------------------------|-----------|

| <b>1</b> | <b>Introduction.....</b>               | <b>9</b>  |

| <b>2</b> | <b>Pin Description.....</b>            | <b>10</b> |

| <b>3</b> | <b>Specification.....</b>              | <b>11</b> |

| 3.1      | Absolute Maximum Ratings.....          | 11        |

| 3.2      | Operating Range.....                   | 11        |

| 3.3      | Characteristics.....                   | 12        |

| <b>4</b> | <b>Operating Modes and States.....</b> | <b>18</b> |

| 4.1      | Operating Modes.....                   | 18        |

| 4.2      | Device states.....                     | 18        |

| 4.3      | State Transitions.....                 | 19        |

| <b>5</b> | <b>Functional Descriptions.....</b>    | <b>20</b> |

| 5.1      | Block Diagram.....                     | 20        |

| 5.2      | Wake-up Controller.....                | 20        |

| 5.3      | System Controller.....                 | 24        |

| 5.4      | Clock Generators.....                  | 24        |

| 5.5      | Core.....                              | 25        |

| 5.6      | Memories.....                          | 32        |

| 5.7      | Power Supply and Reset Generator.....  | 36        |

| 5.8      | Measurement Interface.....             | 36        |

| 5.9      | WAM Interface.....                     | 36        |

| 5.10     | RF transmitter.....                    | 37        |

| 5.11     | RF Transmission Controller.....        | 40        |

| 5.12     | LF Receiver.....                       | 41        |

| 5.13     | I/O-Port.....                          | 43        |

| <b>6</b> | <b>Application Circuit.....</b>        | <b>45</b> |

| <b>7</b> | <b>Package Information.....</b>        | <b>46</b> |

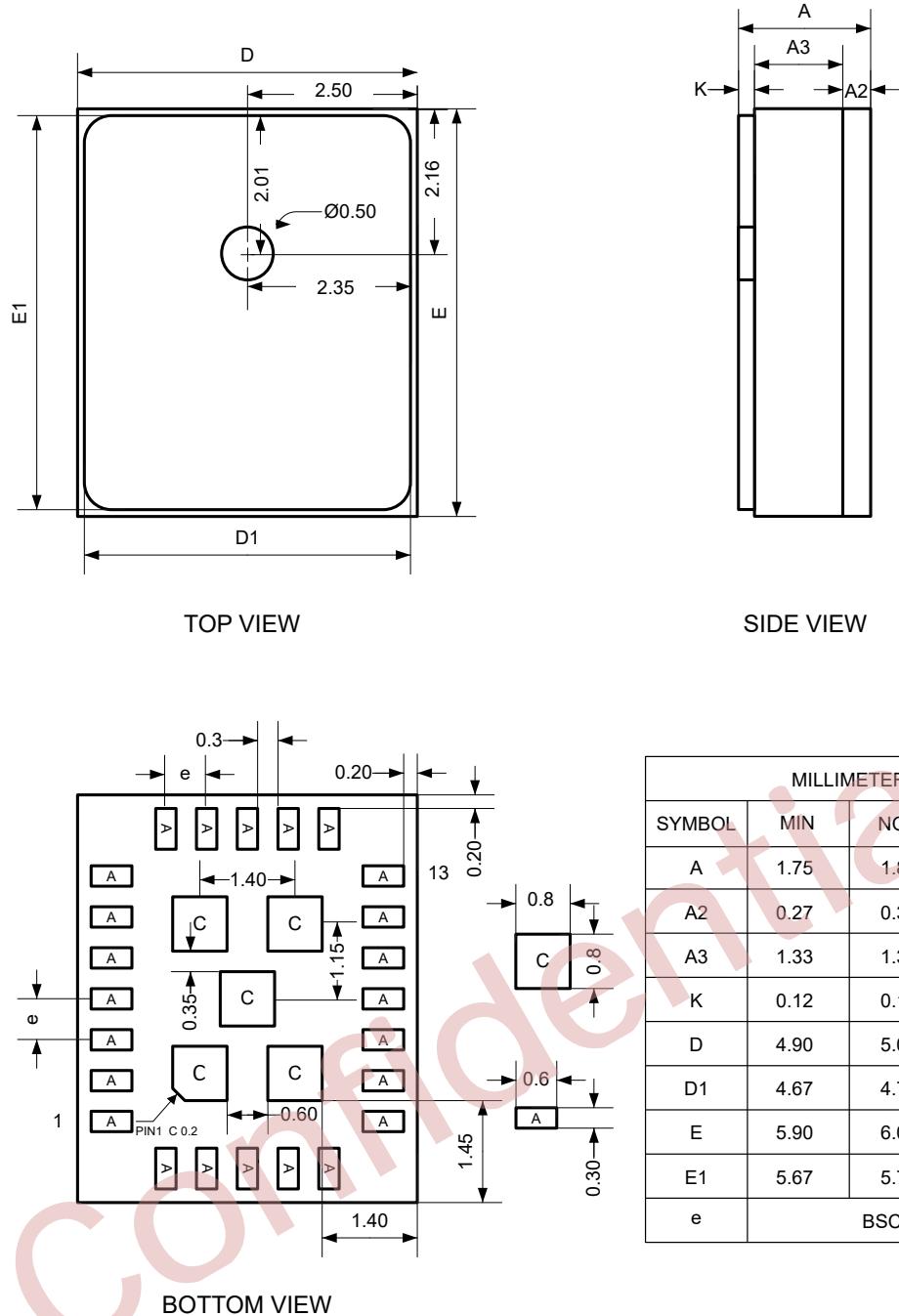

| 7.1      | Package Outline.....                   | 46        |

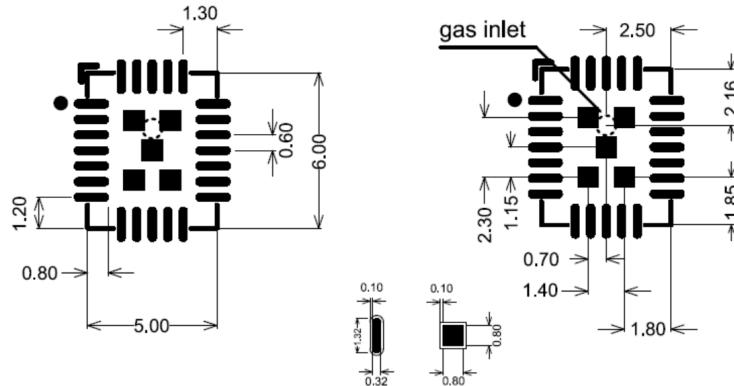

| 7.2      | Footprint.....                         | 47        |

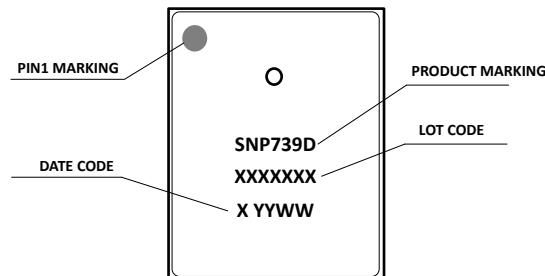

| 7.3      | Marking.....                           | 47        |

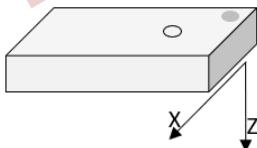

| 7.4      | Accelerometer.....                     | 47        |

| <b>8</b> | <b>Revision History.....</b>           | <b>48</b> |

## List of Tables

|          |                                                    |    |

|----------|----------------------------------------------------|----|

| Table 1  | Order Information.....                             | 9  |

| Table 2  | Pin Description.....                               | 10 |

| Table 3  | Absolute Maximum Ratings.....                      | 11 |

| Table 4  | Operating Range.....                               | 11 |

| Table 5  | Pressure Sensor 900kPa Variant.....                | 12 |

| Table 6  | Pressure Sensor 1900kPa Variant.....               | 12 |

| Table 7  | x-axis Acceleration Sensor.....                    | 12 |

| Table 8  | z-axis Acceleration Sensor.....                    | 13 |

| Table 9  | Temperature Sensor.....                            | 13 |

| Table 10 | Battery Sensor.....                                | 13 |

| Table 11 | Thermal Shutdown.....                              | 13 |

| Table 12 | Digital I/O Pins - Operating Range.....            | 14 |

| Table 13 | Digital I/O Pins - Electrical Characteristics..... | 14 |

| Table 14 | Power On Reset and Battery Monitoring.....         | 14 |

| Table 15 | FLASH Memory.....                                  | 14 |

| Table 16 | Supply Currents at 3.0V Supply Voltage.....        | 14 |

| Table 17 | LF Receiver Characteristics.....                   | 15 |

| Table 18 | RF1 Transmitter Characteristics.....               | 15 |

| Table 19 | RF1 Crystal Oscillator.....                        | 16 |

| Table 20 | Wake-up and power-on timing.....                   | 16 |

| Table 21 | Typical Clock.....                                 | 17 |

| Table 22 | Typical Clock Deviation.....                       | 17 |

| Table 23 | Operating Modes Overview.....                      | 18 |

| Table 24 | Device states overview.....                        | 18 |

| Table 25 | Power management.....                              | 18 |

| Table 26 | Truth Table of Wake-Up I/O Selection.....          | 22 |

| Table 27 | CWDT period config.....                            | 28 |

| Table 28 | UART mode selection.....                           | 30 |

| Table 29 | Lockbyte2 for lock range of FLASH main.....        | 34 |

| Table 30 | Lockbyte2n for lock range of FLASH main.....       | 34 |

| Table 31 | Protected Flash.....                               | 34 |

| Table 32 | Encode format configuration table.....             | 37 |

| Table 33 | PLL frequency output of FSK modulation 24MHz.....  | 38 |

| Table 34 | RF TX baud rate configuration.....                 | 40 |

| Table 35 | GPIOs function definition.....                     | 43 |

---

|                                |    |

|--------------------------------|----|

| Table 36 Revision History..... | 48 |

|--------------------------------|----|

Confidential

## List of Figures

|           |                                                |    |

|-----------|------------------------------------------------|----|

| Figure 1  | Pin Configuration(Top View).....               | 10 |

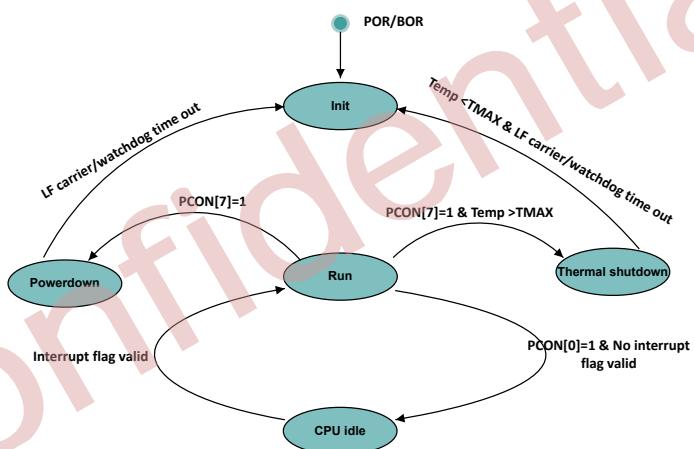

| Figure 2  | State transitions.....                         | 19 |

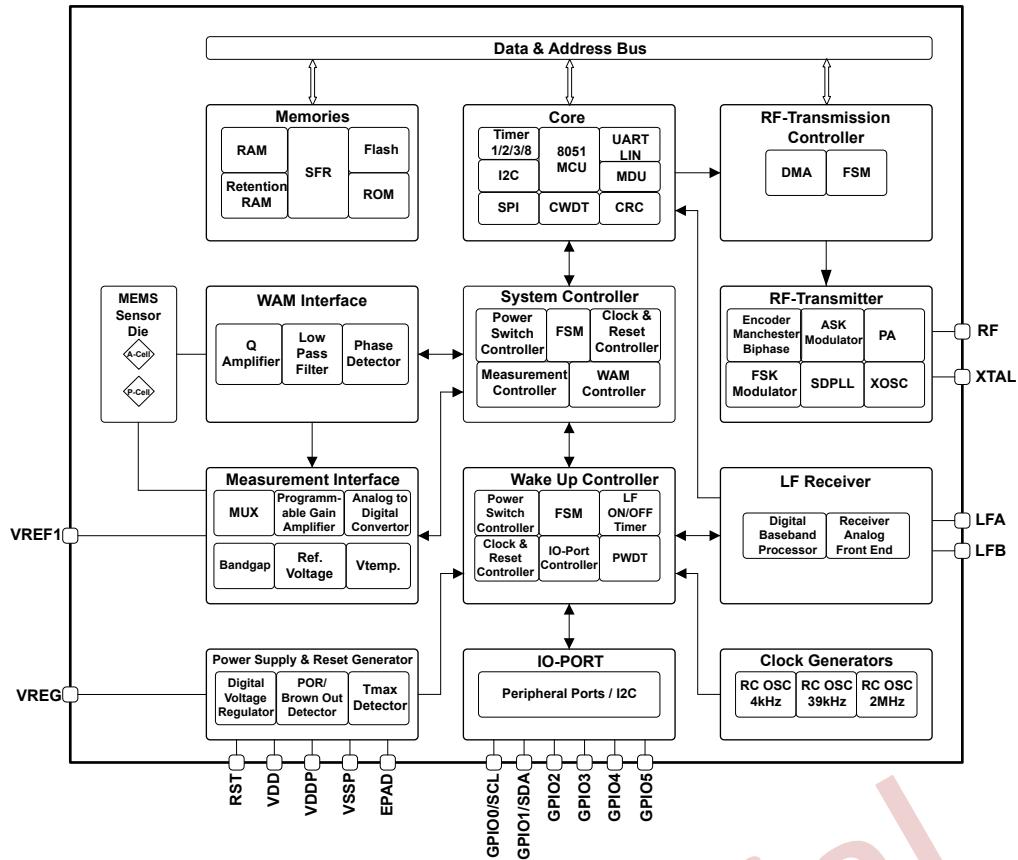

| Figure 3  | Block Diagram.....                             | 20 |

| Figure 4  | Power-On and Under-Voltage Reset Behavior..... | 23 |

| Figure 5  | Clock distribution diagram.....                | 25 |

| Figure 6  | Memory map.....                                | 33 |

| Figure 7  | RAM/SFR map.....                               | 36 |

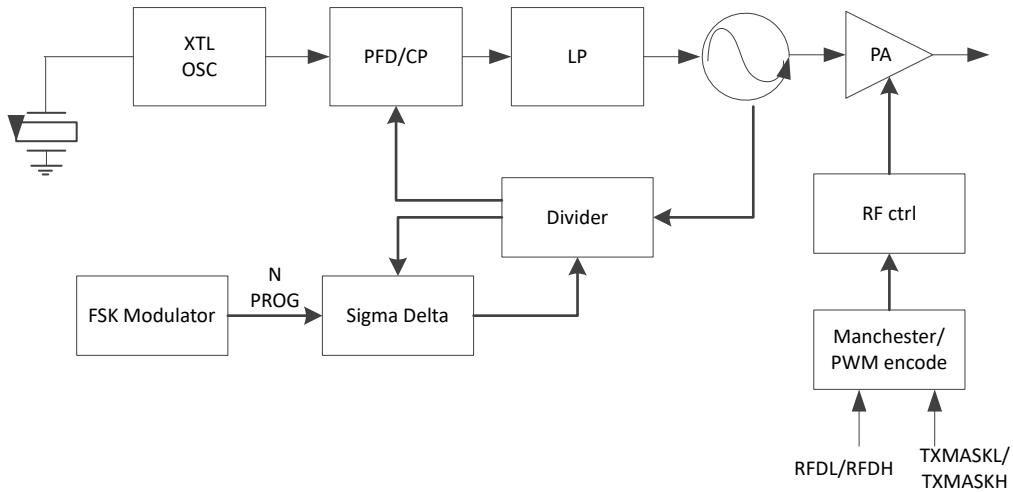

| Figure 8  | RF1 transmitter block.....                     | 37 |

| Figure 9  | RF encoder.....                                | 38 |

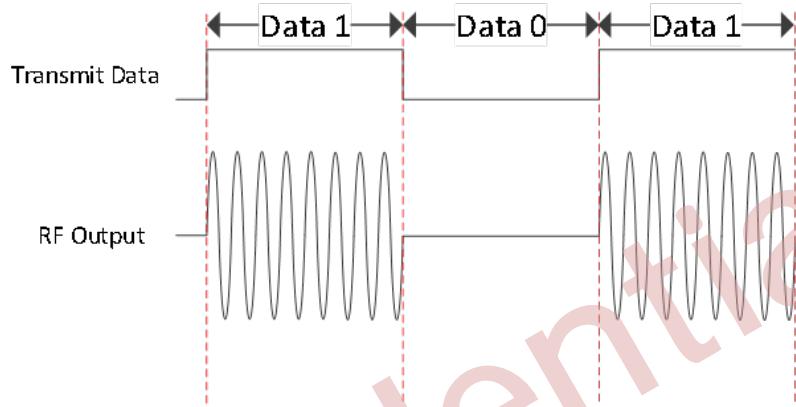

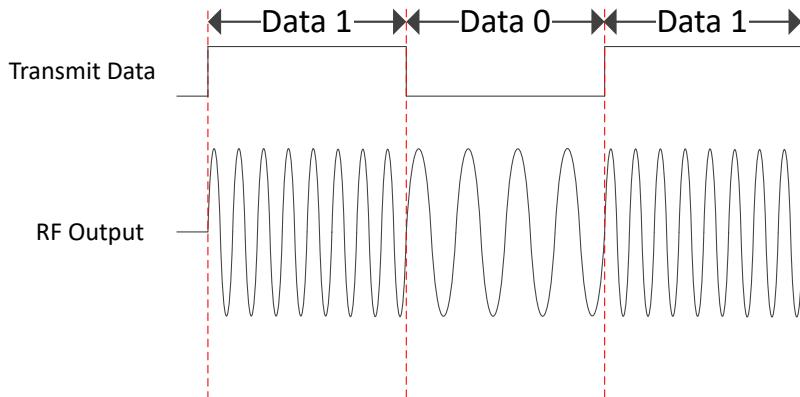

| Figure 10 | ASK modulation.....                            | 39 |

| Figure 11 | FSK modulation.....                            | 40 |

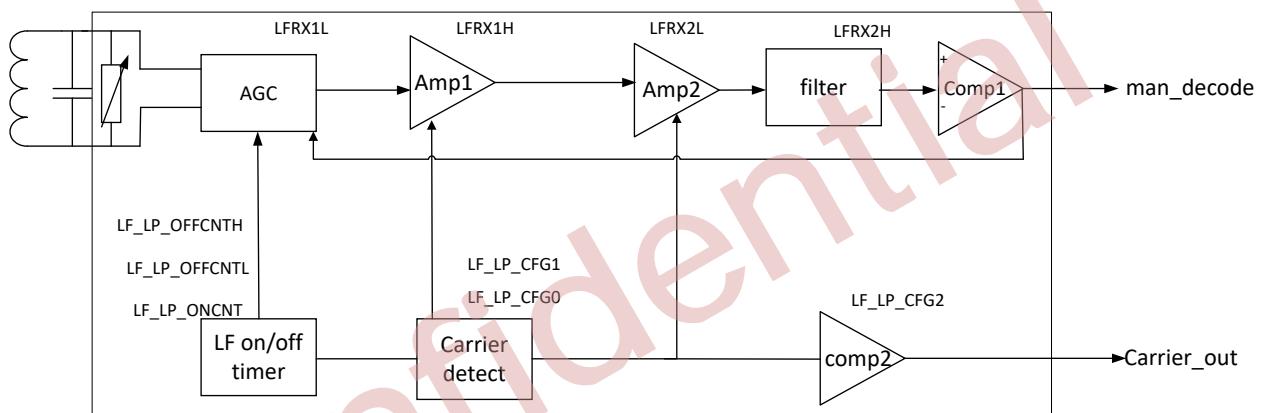

| Figure 12 | AFE.....                                       | 41 |

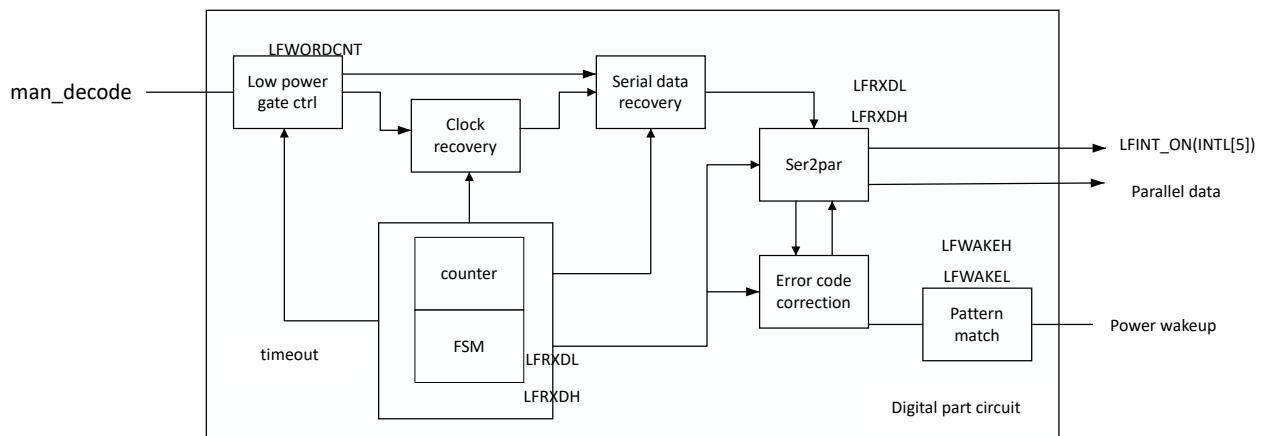

| Figure 13 | LF digital baseband block diagram.....         | 42 |

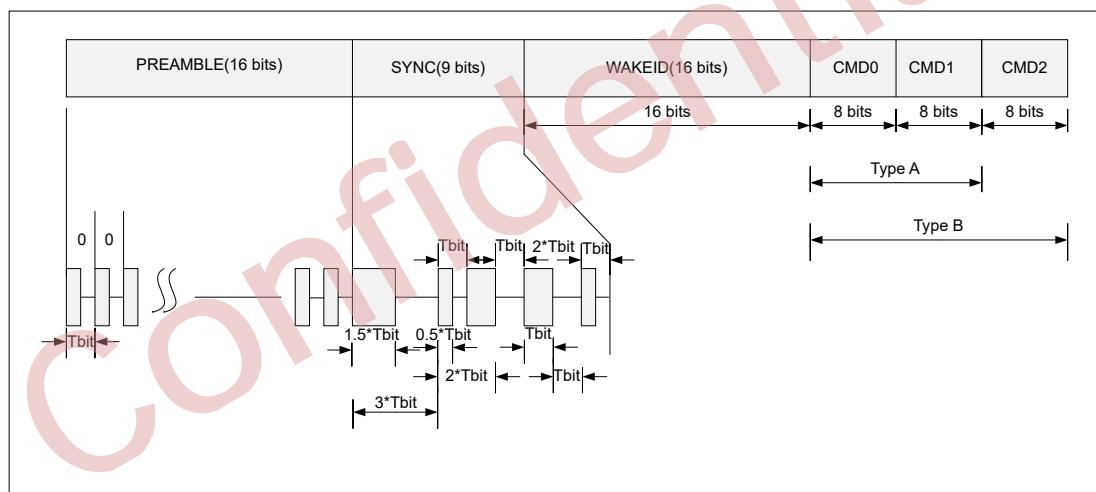

| Figure 14 | LF telegram.....                               | 42 |

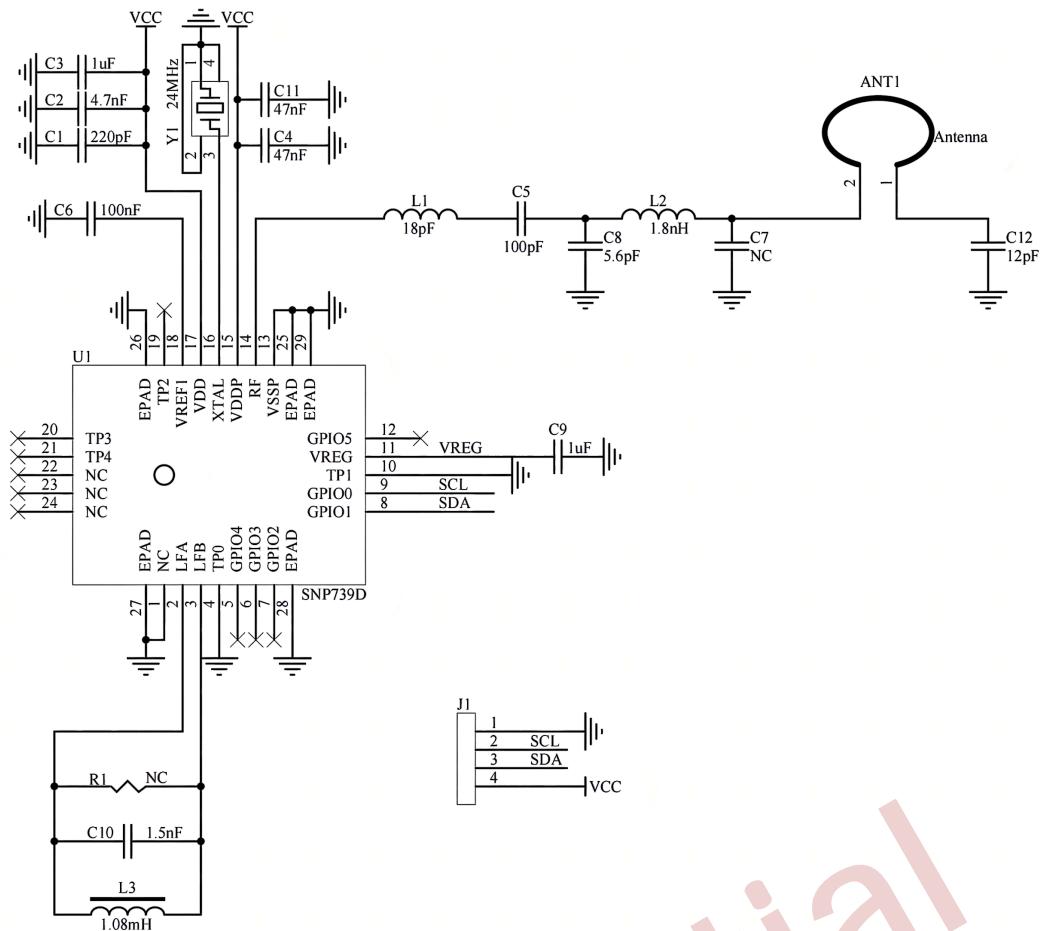

| Figure 15 | Application Circuit.....                       | 45 |

| Figure 16 | Package Outline.....                           | 46 |

| Figure 17 | Recommend footprint layout.....                | 47 |

| Figure 18 | Marking information.....                       | 47 |

| Figure 19 | Acceleration sensor direction.....             | 47 |

Confidential

**List of Abbreviations (keyword:TPMS )**

| Abbreviations | Full spelling                               |

|---------------|---------------------------------------------|

| PA            | Power Amplifier                             |

| AON           | Always Online                               |

| LGA           | Land Grid Array                             |

| WAM           | Wheel Auto Mapping                          |

| MCU           | Microcontroller Unit                        |

| FLASH         | Flash Memory                                |

| ADC           | Analog to Digital Converter                 |

| RAM           | Random Access Memory                        |

| RF            | Radio Frequency                             |

| LF            | Low Frequency                               |

| UART          | Universal Asynchronous Receiver/Transmitter |

| SPI           | Serial Peripheral Interface                 |

| I2C           | Inter Integrated Circuit                    |

| TPMS          | Tire Pressure Monitoring System             |

| MEMS          | Micro Electromechanical System              |

| ASK           | Amplitude Shift Keying                      |

| FSK           | Frequency Shift Keying                      |

| CRC           | Cyclic Redundancy Check                     |

| POR           | Power On Reset                              |

| BOR           | Brown Out Reset                             |

| XTAL          | External Crystal Oscillator                 |

| SFR           | Special Function Register                   |

| IRAM          | Internal RAM                                |

| XRAM          | External RAM                                |

| PWM           | Pulse Width Modulation                      |

| PLL           | Phase Locked Loop                           |

| CPU           | Central Processing Unit                     |

## 1 Introduction

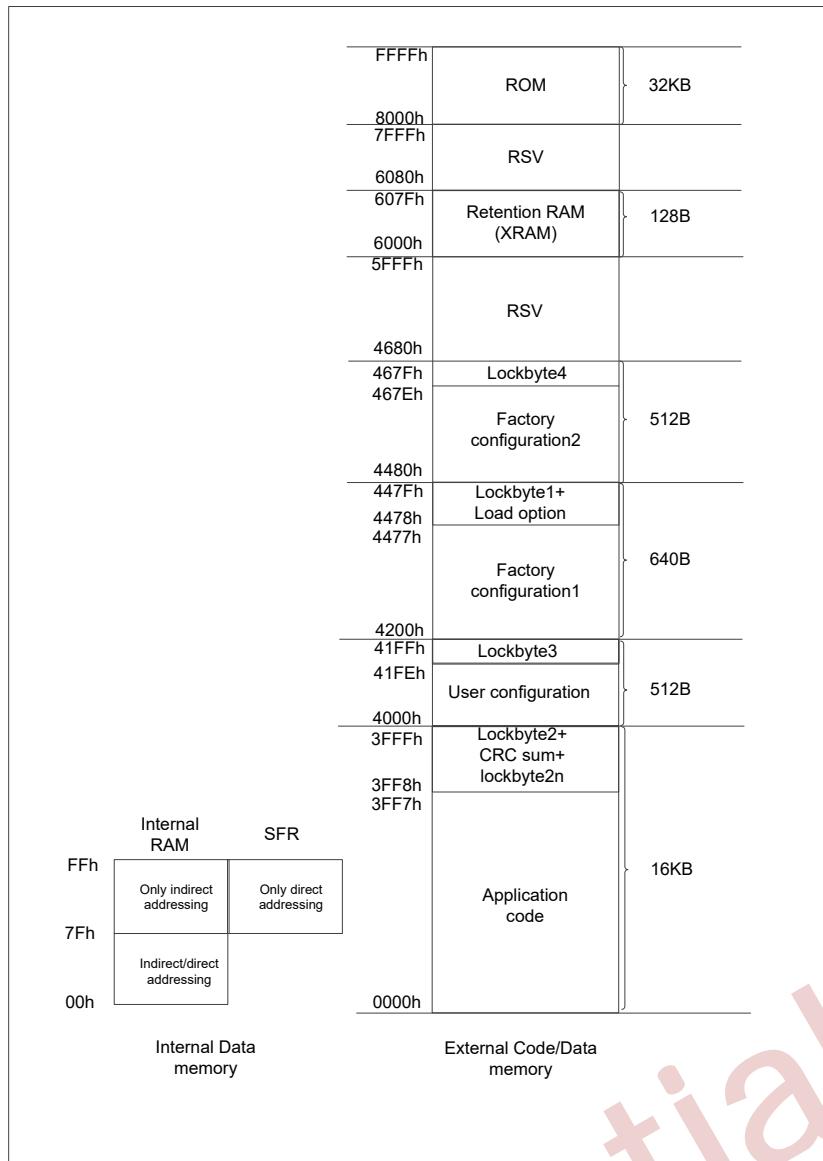

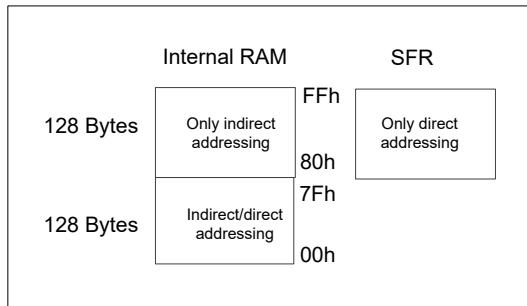

SNP739D consists of 16K Flash memory, 32K ROM memory, interrupt bus, configuration registers and control bus which operate the analogue circuitry all of which are controlled via an 8-bit integrated microcontroller.

The micro is clocked by a tunable oscillator with a selectable center frequency. The motion detection is achieved via accelerometer.

Measurements of pressure, acceleration, temperature, and battery voltage are performed under software control, allowing the application software to format and prepare the data for RF transmission.

A software defined wakeup mechanism is developed for minimizing power consumption. An Interval timer controls the timing of measurements and transmissions.

For smart manage SNP739D workload, accelerometer motion and phase location detection integrated in SNP739D. And both tire roll status detection and WAM are supported, with no addition accelerometer need.

Embedded LF receiver can help SNP739D to wake up at regular intervals and it works independently with no CPU aids at any time of user definition timeout period, thus helps power saving greatly. The LF receiver supports wireless Flash programming to the chip without I2C communication which demonstrates high efficiency in customer firmware development phase. The integrated microcontroller's instruction set is compatible to the standard 8051 processor. It is equipped with hardware Manchester, bi-phase encoder/decoder and CRC generator and checker, which enable easy implementations of customer specific applications.

The low-power RF Transmitter for 315 and 434 MHz contains a fully integrated PLL synthesizer, an ASK/FSK modulator and an efficient power amplifier.

On-chip Flash memory stores the customer specific application program code, the unique ID-number and the calibration data for the sensor. Additionally, the embedded library functions developed by SENASIC cover standard tasks used by the application.

Table 1-1 Order Information

| Model        | Pressure Range | Package | Packing Option |

|--------------|----------------|---------|----------------|

| SNP739D01CLE | 100 ~ 900      | LGA24   | 3000ea/Reel    |

| SNP739D02CLE | 100 ~ 1900     |         | 3000ea/Reel    |

## 2 Pin Description

**Figure 2-1 Pin Configuration(Top View)**

**Table 2-1 Pin Description**

| Pin No. | Name  | Pin Type   | Function                                                            |

|---------|-------|------------|---------------------------------------------------------------------|

| 1       | NC    |            | Connect to GND                                                      |

| 2       | LFA   | Analog IO  | LF channel coil connection                                          |

| 3       | LFB   | Analog IO  | LF channel coil connection                                          |

| 4       | TP0   |            | Connect to GND                                                      |

| 5       | GPIO4 | Digital IO | GPIO/SPI MISO/UART RXD                                              |

| 6       | GPIO3 | Digital IO | GPIO/SPI MOSI/UART TXD                                              |

| 7       | GPIO2 | Digital IO | GPIO/SPI CSN                                                        |

| 8       | GPIO1 | Digital IO | GPIO/I2C data                                                       |

| 9       | GPIO0 | Digital IO | GPIO/I2C Clock                                                      |

| 10      | TP1   |            | Connect to GND                                                      |

| 11      | VREG  | Supply     | Internal regulator, it must not be used as external current source. |

| 12      | GPIO5 | Digital IO | GPIO/SPI CLK                                                        |

| 13      | VSSP  | Supply     | Ground                                                              |

| 14      | RF    | Analog IO  | RF output                                                           |

| 15      | VDDP  | Supply     | Battery supply 3V                                                   |

| 16      | XTAL  | Analog IO  | XTAL pin                                                            |

| 17      | VDD   | Supply     | Battery supply 3V                                                   |

| 18      | VREF1 | Analog IO  | 100nF to ground                                                     |

| 19      | TP2   |            | N.C., just place a test point on board                              |

| 20      | TP3   |            | N.C., just place a test point on board                              |

| 21      | TP4   |            | N.C., just place a test point on board                              |

| 22      | NC    |            | Not connect                                                         |

| 23      | NC    |            | Not connect                                                         |

| 24      | NC    |            | Not connect                                                         |

| 25~29   | GND   | Supply     | Ground                                                              |

### 3 Specification

#### 3.1 Absolute Maximum Ratings

Table 3-1 Absolute Maximum Ratings

| Parameter                    | Symbol           | Values |      |              | Unit | Note/Test Condition                                                                        |

|------------------------------|------------------|--------|------|--------------|------|--------------------------------------------------------------------------------------------|

|                              |                  | Min.   | Typ. | Max.         |      |                                                                                            |

| Max. Supply Voltage          | $V_{DDmax}$      | -0.3   |      | +3.8         | V    |                                                                                            |

| ESD robustness HBM           | $V_{ESD\_HBM}$   | -2000  |      | +2000        | V    | All pins according to JS-001-2014                                                          |

|                              |                  | -4000  |      | +4000        | V    | RF pin according to JS-001-2014                                                            |

| ESD robustness CDM           | $V_{ESD\_CDM}$   | -500   |      | +500         | V    | All pins according to JS-002-2014                                                          |

| Latch up                     | $I_{LU}$         | -100   |      | +100         | mA   | All pins according to JEDEC 78D                                                            |

| Input Voltage                | $V_{in}$         | -0.3   |      | $V_{DD}+0.3$ | V    | GPIO0~ GPIO5                                                                               |

|                              |                  | -0.3   |      | $V_{DD}+0.3$ | V    | XTAL                                                                                       |

|                              |                  | -0.3   |      | $V_{DD}+0.3$ | V    | LFA, LFB                                                                                   |

| Dynamic voltage at RF pin    | $V_{dyn\_PAOUT}$ |        |      | $V_{DD}+0.3$ | V    |                                                                                            |

| DC current                   | $I_{DC}$         | -10    |      | +10          | mA   | GPIO0~ GPIO5                                                                               |

|                              |                  | -10    |      | +10          | mA   | XTAL                                                                                       |

|                              |                  | -10    |      | +10          | mA   | LFA, LFB                                                                                   |

| Input pressure               | $P_{in}$         | 0      |      | 2000         | kPa  |                                                                                            |

|                              |                  | 2000   |      | 2500         | kPa  | Maximal 2s 5 times over lifetime                                                           |

| Constant Acceleration        | $a_{CA}$         |        |      | 3500         | g    | Tested in +/- x,y,z- direction.(Device unpowered)                                          |

| Mechanical Shock             | $a_{MS}$         |        |      | 6000         | g    | 0.3 ms half sine pulses. 5 shocks in +/- x,y,z-direction, respectively. (Device unpowered) |

| Variable Frequency Vibration | $f_{VFV}$        | 20     |      | 2000         | Hz   | Tested in +/- x,y,z- direction,50 g peak acceleration.                                     |

| Package Drop                 | $h_{Drop}$       |        |      | 1.2          | m    | Drop part on each of 6 axes once from a height of 1.2m onto a concrete surface.            |

#### 3.2 Operating Range

Table 3-2 Operating Range

| Parameter           | Symbol          | Values |      |      | Unit | Note/Test Condition       |

|---------------------|-----------------|--------|------|------|------|---------------------------|

|                     |                 | Min.   | Typ. | Max. |      |                           |

| Supply Voltage      | $V_{DD}$        | 2.1    | 3.0  | 3.6  | V    |                           |

| Ambient Temperature | $T_{operating}$ | -40    |      | 125  | °C   | Normal operation          |

|                     | $T_{Flash}$     | -40    |      | 125  | °C   | Flash programming/erasing |

|                     | $T_{Flash}$     | -50    |      | 150  | °C   | Without power             |

### 3.3 Characteristics

#### 3.3.1 Pressure Sensor

**Table 3-3 Pressure Sensor 900kPa Variant**

| Parameter            | Symbol                 | Values |      |      | Unit    | Note/Test Condition           |

|----------------------|------------------------|--------|------|------|---------|-------------------------------|

|                      |                        | Min.   | Typ. | Max. |         |                               |

| Input Pressure Range | $P_{in,H}$             | 100    |      | 900  | kPa     |                               |

| ADC Resolution       | $P_{ADC\_res,H}$       |        |      | 1.1  | kPa/LSB |                               |

| Random Error         | $P_{random,H}$         | -2.3   |      | 2.3  | kPa     | 95% of all measurements       |

| Measurement Error    | $P_{Error\ 100-500,H}$ | -5     |      | 5    | kPa     | 0°C to +70°C                  |

|                      |                        | -10    |      | 10   | kPa     | -40°C to 0°C, +70°C to +125°C |

|                      | $P_{Error\ 500-900,H}$ | -7     |      | 7    | kPa     | 0°C to +70°C                  |

|                      |                        | -15    |      | 15   | kPa     | -40°C to 0°C, +70°C to +125°C |

**Table 3-4 Pressure Sensor 1900kPa Variant**

| Parameter                              | Symbol                  | Values |      |      | Unit    | Note/Test Condition           |

|----------------------------------------|-------------------------|--------|------|------|---------|-------------------------------|

|                                        |                         | Min.   | Typ. | Max. |         |                               |

| Input Pressure Range                   | $P_{in,N}$              | 100    |      | 1900 | kPa     |                               |

| ADC Resolution                         | $P_{ADC\_res,N}$        |        |      | 1.6  | kPa/LSB |                               |

| Random Error                           | $P_{random,N}$          | -3.3   |      | 3.3  | kPa     | 95% of all measurements       |

| Input Pressure Range<br>ADC Resolution | $P_{Error\ 100-500,N}$  | -7     |      | 7    | kPa     | 0°C to +70°C                  |

|                                        |                         | -15    |      | 15   | kPa     | -40°C to 0°C, +70°C to +125°C |

|                                        |                         | -12    |      | 12   | kPa     | 0°C to +70°C                  |

|                                        | $P_{Error\ 500-900,N}$  | -25    |      | 25   | kPa     | -40°C to 0°C, +70°C to +125°C |

|                                        |                         | -20    |      | 20   | kPa     | 0°C to +70°C                  |

|                                        | $P_{Error\ 900-1500,N}$ | -40    |      | 40   | kPa     | -40°C to 0°C, +70°C to +125°C |

#### 3.3.2 x/z-axis Acceleration Sensor

**Table 3-5 x-axis Acceleration Sensor**

| Parameter                | Symbol           | Values |      |      | Unit  | Note/Test Condition                                 |

|--------------------------|------------------|--------|------|------|-------|-----------------------------------------------------|

|                          |                  | Min.   | Typ. | Max. |       |                                                     |

| Input acceleration Range | $a_{in,x}$       | -120   |      | 120  | g     |                                                     |

| Total Acceleration Error | $a_{err\_tot,x}$ | -3     |      | +3   | g     | $ a_{in}  < 20g, -40°C \leq T \leq 90°C$            |

|                          |                  | -5     |      | +5   | g     | $ a_{in}  < 20g, 90°C \leq T \leq 125°C$            |

|                          |                  | -7     |      | +7   | g     | $20g \leq  a_{in}  < 100g, -40°C \leq T \leq 90°C$  |

|                          |                  | -9     |      | +9   | g     | $20g \leq  a_{in}  < 100g, 90°C \leq T \leq 125°C$  |

|                          |                  | -11    |      | +11  | g     | $100g \leq  a_{in}  < 120g, -40°C \leq T \leq 90°C$ |

|                          |                  | -13    |      | +13  | g     | $100g \leq  a_{in}  < 120g, 90°C \leq T \leq 125°C$ |

| Random error             | $a_{random,x}$   | -0.2   |      | +0.2 | g     | 99.8% of all measurements, $ a_{in}  = 0$           |

| ADC resolution           | $a_{ADC\_res,x}$ |        |      | 0.07 | g/LSB | 1 LSB corresponds to 0.07 g or less                 |

Table 3-6 z-axis Acceleration Sensor

| Parameter                | Symbol           | Values |      |       | Unit  | Note/Test Condition                                            |

|--------------------------|------------------|--------|------|-------|-------|----------------------------------------------------------------|

|                          |                  | Min.   | Typ. | Max.  |       |                                                                |

| Input acceleration Range | $a_{in,z}$       | -250   |      | 250   | g     |                                                                |

| Total Acceleration Error | $a_{err\_tot,z}$ | -3     |      | +3    | g     | $ a_{in}  < 20g, -40^{\circ}C \leq T < 90^{\circ}C$            |

|                          |                  | -5     |      | +5    | g     | $ a_{in}  < 20g, 90^{\circ}C \leq T < 125^{\circ}C$            |

|                          |                  | -7     |      | +7    | g     | $20g \leq  a_{in}  < 100g, -40^{\circ}C \leq T < 90^{\circ}C$  |

|                          |                  | -9     |      | +9    | g     | $20g \leq  a_{in}  < 100g, 90^{\circ}C \leq T < 125^{\circ}C$  |

|                          |                  | -11    |      | +11   | g     | $100g \leq  a_{in}  < 200g, -40^{\circ}C \leq T < 90^{\circ}C$ |

|                          |                  | -13    |      | +13   | g     | $100g \leq  a_{in}  < 200g, 90^{\circ}C \leq T < 125^{\circ}C$ |

|                          |                  | -20    |      | +20   | g     | $200g \leq  a_{in}  < 250g, -40^{\circ}C \leq T < 90^{\circ}C$ |

|                          |                  | -22    |      | +22   | g     | $200g \leq  a_{in}  < 250g, 90^{\circ}C \leq T < 125^{\circ}C$ |

| Random error             | $a_{random,z}$   | -0.3   |      | +0.3  | g     | 99.8% of all measurements, $ a_{in} =0$                        |

| ADC resolution           | $a_{ADC\_res,z}$ |        |      | 0.125 | g/LSB | 1 LSB corresponds to 0.125 g or less                           |

### 3.3.3 Temperature Sensor

Table 3-7 Temperature Sensor

| Parameter         | Symbol       | Values |      |      | Unit | Note/Test Condition                             |

|-------------------|--------------|--------|------|------|------|-------------------------------------------------|

|                   |              | Min.   | Typ. | Max. |      |                                                 |

| Measurement range | $T_{range}$  | -40    |      | +125 | °C   |                                                 |

| Measurement error | $T_{Error}$  | -5     |      | +5   | °C   | $-40 \dots -10^{\circ}C, V_{DD}=2.1 \dots 3.6V$ |

|                   |              | -3     |      | +3   | °C   | $-10 \dots 90^{\circ}C, V_{DD}=2.1 \dots 3.6V$  |

|                   |              | -5     |      | +5   | °C   | $90 \dots +125^{\circ}C, V_{DD}=2.1 \dots 3.6V$ |

| Random error      | $T_{random}$ | -1     |      | +1   | °C   |                                                 |

### 3.3.4 Battery Sensor

Table 3-8 Battery Sensor

| Parameter         | Symbol      | Values |      |      | Unit | Note/Test Condition             |

|-------------------|-------------|--------|------|------|------|---------------------------------|

|                   |             | Min.   | Typ. | Max. |      |                                 |

| Measurement range | $V_{range}$ | 2.1    |      | 3.6  | V    |                                 |

| Measurement Error | $V_{Error}$ | -3     |      | +3   | %    | Percentage of measurement value |

### 3.3.5 Thermal Shutdown

Table 3-9 Thermal Shutdown

| Parameter                      | Symbol       | Values |      |      | Unit | Note/Test Condition |

|--------------------------------|--------------|--------|------|------|------|---------------------|

|                                |              | Min.   | Typ. | Max. |      |                     |

| Thermal Shutdown HOT threshold | $T_{HOT,TH}$ |        |      | 125  | °C   |                     |

| Thermal shutdown HOT release   | $T_{HOT,RE}$ | 110    |      |      | °C   |                     |

| Hysteresis                     | $T_{HYST}$   |        | 10   |      | °C   |                     |

### 3.3.6 General Purpose Digital I/O Pins

**Table 3-10 Digital I/O Pins - Operating Range**

| Parameter                      | Symbol        | Values      |      |             | Unit | Note/Test Condition |

|--------------------------------|---------------|-------------|------|-------------|------|---------------------|

|                                |               | Min.        | Typ. | Max.        |      |                     |

| Digital Pin Output Current     | $I_{in\ DIG}$ | -4          |      | 4           | mA   | Pins GPIO0~ GPIO5   |

| Digital Pin Input High Voltage | $V_{IH}$      | $0.8V_{DD}$ |      |             | V    | functional          |

| Digital Pin Input Low Voltage  | $V_{IL}$      |             |      | $0.2V_{DD}$ | V    | functional          |

**Table 3-11 Digital I/O Pins - Electrical Characteristics**

| Parameter                       | Symbol   | Values      |      |             | Unit | Note/Test Condition  |

|---------------------------------|----------|-------------|------|-------------|------|----------------------|

|                                 |          | Min.        | Typ. | Max.        |      |                      |

| Digital Pin-Output High Voltage | $V_{OH}$ | $0.8V_{DD}$ |      |             | V    |                      |

| Digital Pin-Output Low Voltage  | $V_{OL}$ |             |      | $0.2V_{DD}$ | V    | at 4 mA load current |

| Digital Pin Input Capacitance   | $C_{in}$ |             |      | 10          | pF   |                      |

### 3.3.7 Power On Reset and Battery Monitoring

**Table 3-12 Power On Reset and Battery Monitoring**

| Parameter                           | Symbol     | Values |      |      | Unit | Note/Test Condition |

|-------------------------------------|------------|--------|------|------|------|---------------------|

|                                     |            | Min.   | Typ. | Max. |      |                     |

| Power on Reset level                | $V_{POR}$  | 1.0    |      | 1.6  | V    |                     |

| Power On Reset Release Level        | $V_{THR}$  | 1.1    |      | 1.7  | V    |                     |

| Low Battery Threshold Warning Level | $V_{LBAT}$ | 2.2    | 2.3  | 2.4  | V    |                     |

### 3.3.8 FLASH Memory

**Table 3-13 FLASH Memory**

| Parameter                        | Symbol            | Values |      |      | Unit | Note/Test Condition                                                      |

|----------------------------------|-------------------|--------|------|------|------|--------------------------------------------------------------------------|

|                                  |                   | Min.   | Typ. | Max. |      |                                                                          |

| Flash memory data retention time | $t_{Ret\ Flash}$  | 10     |      |      | y    | Defect rate < 1ppm over lifetime for typical mission temperature profile |

| Flash write cycles               | $N_{write}$       | 1000   |      |      |      |                                                                          |

| Flash page write time            | $t_{write\_line}$ |        |      | 7.6  | ms   | Including time for verification. I2C Baud rate = 400 kbit/s              |

### 3.3.9 Supply Currents

**Table 3-14 Supply Currents at 3.0V Supply Voltage**

| Parameter                         | Symbol         | Values |      |      | Unit    | Note/Test Condition |

|-----------------------------------|----------------|--------|------|------|---------|---------------------|

|                                   |                | Min.   | Typ. | Max. |         |                     |

| Supply current in Powerdown state | $I_{PWD\_3V}$  |        | 0.2  | 0.3  | $\mu A$ | +25°C               |

|                                   |                |        | 2.6  | 4.5  | $\mu A$ | +125°C              |

|                                   |                |        |      | 0.5  | $\mu A$ | -40°C               |

| Supply current in CPU idle state  | $I_{IDLE\_3V}$ |        |      | 20   | $\mu A$ | +25°C               |

|                                   |                |        | 88   | 152  | $\mu A$ | +125°C              |

|                                   |                |        |      | 64   | $\mu A$ | -40°C               |

| Parameter                                                     | Symbol         | Values |       |      | Unit | Note/Test Condition |

|---------------------------------------------------------------|----------------|--------|-------|------|------|---------------------|

|                                                               |                | Min.   | Typ.  | Max. |      |                     |

| Supply current in Run state                                   | $I_{RUN\_3V}$  |        | 0.631 |      | mA   | +25°C               |

|                                                               |                |        | 0.705 |      | mA   | +125°C              |

|                                                               |                |        | 0.610 |      | mA   | -40°C               |

| Supply current in Thermal shutdown state                      | $I_{TSHD\_3V}$ |        | 2.8   | 4.6  | μA   | +125°C              |

| Supply current in LF carrier detection mode                   | $I_{LFCD\_3V}$ |        |       | 9    | μA   | +25°C               |

|                                                               |                |        |       | 12   | μA   | +125°C              |

|                                                               |                |        |       | 8    | μA   | -40°C               |

| Supply current in LF data reception mode                      | $I_{LF\_3V}$   |        | 10.2  | 12   | μA   | +25°C               |

|                                                               |                |        | 14.5  | 16   | μA   | +125°C              |

|                                                               |                |        | 9.6   | 11   | μA   | -40°C               |

| Supply current at RF@433MHz - transmission(CW or FSK;CPU off) | $I_{RFTX\_3V}$ |        | 5.5   |      | mA   | +25°C @5dBm         |

|                                                               |                |        | 8.0   |      | mA   | +25°C @8dBm         |

|                                                               |                |        | 11.0  |      | mA   | +25°C @10dBm        |

|                                                               |                |        | 5.2   |      | mA   | +125°C@5dBm         |

|                                                               |                |        | 7.6   |      | mA   | +125°C@8dBm         |

|                                                               |                |        | 10.5  |      | mA   | +125°C@10dBm        |

|                                                               |                |        | 5.8   |      | μA   | -40°C@5dBm          |

|                                                               |                |        | 8.4   |      | mA   | -40°C@8dBm          |

|                                                               |                |        | 11.7  |      | mA   | -40°C@10dBm         |

### 3.3.10 LF Receiver

Table 3-15 LF Receiver Characteristics

| Parameter                                | Symbol         | Values |      |      | Unit   | Note/Test Condition     |

|------------------------------------------|----------------|--------|------|------|--------|-------------------------|

|                                          |                | Min.   | Typ. | Max. |        |                         |

| LF Carrier Frequency <sup>[1]</sup>      | $f_{LF}$       | 118    | 125  | 131  | kHz    |                         |

| LF Data Rate                             | $DR_{LF}$      | 3.8    | 3.9  | 4.1  | kbit/s |                         |

|                                          |                | 6.2    | 6.5  | 6.8  | kbit/s |                         |

| Input differential capacitance           | $C_{LF\ diff}$ | 2.6    | 4    | 9    | pF     | at 125kHz               |

| Input differential resistance            | $R_{LF\ diff}$ | 1      |      |      | MΩ     |                         |

| LF Receiver settling time after power on | $t_{ON\_Set.}$ |        |      | 5    | ms     | After receiver power-on |

| LF Detection Sensitivity                 | $S_{nodef.}$   | 0.1    |      |      | mVpp   |                         |

|                                          | $S_{det.}$     |        |      | 2    | mVpp   |                         |

Note: [1] LF sensitivity levels are only valid for the specified carrier frequency range.

### 3.3.11 RF Transmitter

Table 3-16 RF1 Transmitter Characteristics

| Parameter          | Symbol                | Values |      |      | Unit | Note/Test Condition |

|--------------------|-----------------------|--------|------|------|------|---------------------|

|                    |                       | Min.   | Typ. | Max. |      |                     |

| Transmit Frequency | $f_{TX,433M,XTAL24M}$ | 432    |      | 444  | MHz  | XTAL 24MHz          |

|                    | $f_{TX,433M,XTAL26M}$ | 433.3  |      | 442  | MHz  | XTAL 26MHz          |

| Parameter                            | Symbol                | Values |       |          | Unit   | Note/Test Condition                                                                |

|--------------------------------------|-----------------------|--------|-------|----------|--------|------------------------------------------------------------------------------------|

|                                      |                       | Min.   | Typ.  | Max.     |        |                                                                                    |

| Output Power transformed into 50 ohm | $f_{TX,433M,XTAL16M}$ | 432    |       | 448      | MHz    | XTAL 16MHz                                                                         |

|                                      | $f_{TX,315M,XTAL24M}$ | 312    |       | 324      | MHz    | XTAL 24MHz                                                                         |

|                                      | $f_{TX,315M,XTAL26M}$ | 312    |       | 325      | MHz    | XTAL 26MHz                                                                         |

|                                      | $f_{TX,315M,XTAL16M}$ | 312    |       | 320      | MHz    | XTAL 16MHz                                                                         |

| Output Power change over temp        | $P_{O,L1,433.92MHz}$  |        | 5.6   |          | dBm    | $V_{bat}=3.0V, T=25^{\circ}C, Z_{load}=50 \text{ ohm}$<br>RF matched Power Level=1 |

|                                      | $P_{O,L2,433.92MHz}$  |        | 7.7   |          | dBm    | $V_{bat}=3.0V, T=25^{\circ}C, Z_{load}=50 \text{ ohm}$<br>RF matched Power Level=2 |

|                                      | $P_{O,L3,433.92MHz}$  |        | 9.8   |          | dBm    | $V_{bat}=3.0V, T=25^{\circ}C, Z_{load}=50 \text{ ohm}$<br>RF matched Power Level=3 |

| Output Power change over supply      | $dP_{-40^{\circ}C}$   |        | 0.6   |          | dB     | $V_{bat}=3.0V, T=-40^{\circ}C$                                                     |

|                                      | $dP_{125^{\circ}C}$   |        | -1.1  |          | dB     | $V_{bat}=3.0V, T=125^{\circ}C$                                                     |

|                                      | $dP_{1.9V}$           | -10.1  | -7.1  |          | dB     | $V_{bat}=1.9V, T=25^{\circ}C$                                                      |

| RF Datarate                          | $dP_{2.1V}$           | -5.5   | -4.8  |          | dB     | $V_{bat}=2.1V, T=25^{\circ}C$                                                      |

|                                      | $dP_{3.6V}$           | 1.6    | 1.9   |          | dB     | $V_{bat}=3.6V, T=25^{\circ}C$                                                      |

| RF Datarate                          | $DR_{RF}$             |        |       | 19.6     | Kbit/s | Manchester coded                                                                   |

| RF Data Rate tolerance               | $dDR_{RF}$            | -1     |       | +1       | %      |                                                                                    |

| FSK frequency shift                  |                       |        | +/-45 | $\pm 70$ | KHz    | Programmable                                                                       |

| RF Data Duty Cycle                   | $DC_{RF,ASK}$         | 45     | 50    | 55       | %      | Valid only for ASK or FSK                                                          |

| ASK Mod depth                        | $MD_{RF,ASK}$         | 90     |       |          | %      |                                                                                    |

**Table 3-17 RF1 Crystal Oscillator**

| Parameter                               | Symbol                  | Values |          |      | Unit | Note/Test Condition |

|-----------------------------------------|-------------------------|--------|----------|------|------|---------------------|

|                                         |                         | Min.   | Typ.     | Max. |      |                     |

| Crystal Frequency                       | $f_{XTAL}$              |        | 16/24/26 |      | MHz  |                     |

| Crystal Oscillator startup peak current | $I_{Xtal\_start\_peak}$ | 0.5    |          |      | mA   |                     |

| Crystal Oscillator startup time         | $t_{Xtal\_start}$       |        |          | 2    | ms   |                     |

### 3.3.12 Wake-up and power-on timing

**Table 3-18 Wake-up and power-on timing**

| Parameter                    | Symbol                   | Values |      |      | Unit | Note/Test Condition                                                                     |

|------------------------------|--------------------------|--------|------|------|------|-----------------------------------------------------------------------------------------|

|                              |                          | Min.   | Typ. | Max. |      |                                                                                         |

| Power on time                | $t_{ini}$                |        |      | 15   | ms   | From the power on to the user program began to run                                      |

| Resume from System idle time | $t_{resume}$             |        |      | 100  | μs   | Time from resume event during system-idle to application code execution start.          |

| LF Wake-up time              | $t_{LF \text{ wake-up}}$ |        |      | 5    | ms   | Time from LF wake-up event during power-down to application code execution start.       |

| Watchdog Wake-up time        | $t_{wd \text{ wake-up}}$ |        |      | 5    | ms   | Time from watchdog timer elapsed during power-down to application code execution start. |

### 3.3.13 Typical Clock and Typical Clock Deviation

Table 3-19 Typical Clock

| Parameter     | Symbol          | Clock | Values |        |      | Unit | Note/Test Condition |

|---------------|-----------------|-------|--------|--------|------|------|---------------------|

|               |                 |       | Min.   | Typ.   | Max. |      |                     |

| Typical clock | $I_{clock\_3V}$ | 2M    |        | 1.981  |      | MHz  | +25°C               |

|               |                 | 39K   |        | 38.641 |      | KHz  | +25°C               |

|               |                 | 32K   |        | 31.791 |      | KHz  | +25°C               |

|               |                 | 4K    |        | 3.975  |      | KHz  | +25°C               |

**Note:** Data in the table are calibrated values.

Table 3-20 Typical Clock Deviation

| Parameter               | Symbol          | Clock | Values      |              |                      | Unit | Note/Test Condition |

|-------------------------|-----------------|-------|-------------|--------------|----------------------|------|---------------------|

|                         |                 |       | Typ.(25°C ) | Allowance(d) | Temperature Drift(k) |      |                     |

| Typical clock deviation | $I_{clock\_3V}$ | 2M    | 1.981       | 0.02         | -0.00213             | MHz  | 25°C to -40°C       |

|                         |                 |       | 1.981       | 0.02         | 0.00126              | MHz  | 25°C to 125°C       |

|                         |                 | 39K   | 38.641      | 0.096        | -0.05272             | KHz  | 25°C to -40°C       |

|                         |                 |       | 38.641      | 0.096        | 0.02849              | KHz  | 25°C to 125°C       |

|                         |                 | 32K   | 31.791      | 0.208        | -0.04188             | KHz  | 25°C to -40°C       |

|                         |                 |       | 31.791      | 0.208        | 0.02148              | KHz  | 25°C to 125°C       |

|                         |                 | 4K    | 3.975       | 0.012        | -0.00468             | KHz  | 25°C to -40°C       |

|                         |                 |       | 3.975       | 0.012        | 0.00279              | KHz  | 25°C to 125°C       |

**Note:** Clock deviation formula:

- $f_{osc} = (\text{Typ}(25^\circ\text{C}) \pm d) - (T-25) \cdot k \quad (T < 25)$ ;

- $f_{osc} = (\text{Typ}(25^\circ\text{C}) \pm d) + (T-25) \cdot k \quad (T \geq 25)$ .

## 4 Operating Modes and States

### 4.1 Operating Modes

The SNP739D provides three operating modes: normal mode, debug mode, programming mode/download mode. The operating mode is decided by GPIO0, GPIO1 power strapping. Operating mode will be latched at positive edge of power on reset (POR). And GPIO1, GPIO0 should be held at least 256ms for stable operating mode generation.

**Table 4-1 Operating Modes Overview**

| GPIO1 | GPIO0 | Short Description                             |

|-------|-------|-----------------------------------------------|

| 0     | 1     | Debug mode <sup>[1]</sup>                     |

| 1     | 0     | Programming mode/Download mode <sup>[2]</sup> |

| 1     | 1     | Normal mode <sup>[3]</sup>                    |

| 0     | 0     | Reserved                                      |

**Note:**

[1] Debug mode: used for chip debugging.

[2] Programming /Download mode: Used for firmware download.

[3] Working status in Normal mode: 1.Init. 2.Run. 3.CPU idle. 4.Powerdown. 5.Thermal shutdown.

### 4.2 Device states

In normal operation mode the SNP739D can be switched into several device states which differ in the number of enabled circuit blocks. For lowest power consumption unused blocks are disconnected from power supply, hence not even idle currents remain.

**Table 4-2 Device states overview**

| Device state     | Short description                                                                                                                                                                                   | Important activated blocks                     |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------|

| Init             | Enter Init state when system reset is active.                                                                                                                                                       | See <a href="#">Table 4-3 Power management</a> |

| Run              | Application code execution.                                                                                                                                                                         | See <a href="#">Table 4-3 Power management</a> |

| CPU idle         | CPU clock is stopped to reduce the current consumption, any peripheral interrupt, such as Timer1/Timer2/Timer3/Timer8/SPI/I2C/UART, ADC, RF Transmitter or LF receiver can wakeup CPU to Run state. | See <a href="#">Table 4-3 Power management</a> |

| Powerdown        | No code execution. Device is waiting for a wake-up event. Lowest current consumption.                                                                                                               | See <a href="#">Table 4-3 Power management</a> |

| Thermal shutdown | Once the system enters Shutdown state it would resume running only when the TMAX circuit temperature is below TMAX threshold setting first, then wake-up timer reset is active.                     | See <a href="#">Table 4-3 Power management</a> |

**Table 4-3 Power management**

| Block Name          | Run                          | CPU Idle                     | Powerdown/Shutdown        |

|---------------------|------------------------------|------------------------------|---------------------------|

| POR                 | <a href="#">Active</a>       | Active                       | Active                    |

| Low battery monitor | Active                       | Active                       | Inactive                  |

| TMAX detector       | Inactive/Active (Selectable) | Inactive/Active (Selectable) | <a href="#">Inactive</a>  |

| Voltage regulator   | Active                       | Active                       | <a href="#">No supply</a> |

| Block Name                                                | Run    | CPU Idle | Powerdown/Shutdown           |

|-----------------------------------------------------------|--------|----------|------------------------------|

| Power management/wake-up timer                            | Active | Active   | Active                       |

| CPU                                                       | Active | Inactive | No supply                    |

| Peripheral CRC, I2C,SPI, LIN, UART,LF decoder, RF encoder | Active | Active   | No supply                    |

| Timer 1,2,3,8                                             | Active | Active   | No supply                    |

| 256 Bytes IRAM                                            | Active | Active   | No supply                    |

| 128 Bytes XRAM                                            | Active | Active   | Inactive                     |

| FLASH                                                     | Active | Active   | No supply                    |

| ROM                                                       | Active | Active   | No supply                    |

| Crystal oscillator (24MHz/16MHz/26MHz)                    | Active | Active   | No supply                    |

| 4k/39kHz RC oscillator                                    | Active | Active   | Active                       |

| 2MHz RC oscillator                                        | Active | Active   | No supply                    |

| LF interval timer                                         | Active | Active   | Inactive/Active (Selectable) |

| LF receiver                                               | Active | Active   | Inactive/Active (Selectable) |

| RF transmitter                                            | Active | Active   | No supply                    |

**Note:** **Active:** block is powered, active and keeps its register contents; **Inactive:** block is powered, cannot be used, but keeps its register contents; **No supply:** block is not powered, cannot be used and all register content is lost.

### 4.3 State Transitions

Figure 4-1 shows the possible state transitions in normal mode. The central device state is Run state because only in Run state the state transitions can be configured. Entering other states from Run state is controlled by application code, either by calling firmware functions or setting control bits. State transitions from other states are controlled by hardware events, e.g. timer events or LF receiver events.

Figure 4-1 State transitions

**Note:** The system can be wakeup from CPU idle to Run state by any interrupt.

## 5 Functional Descriptions

### 5.1 Block Diagram

Figure 5-1 Block Diagram

### 5.2 Wake-up Controller

In a typical TPMS application the SNP73X is in Powerdown state most of its lifetime. In Powerdown state, which is triggered by calling the firmware function `LIB_PDWN_MODE()`, the device is controlled only by the wake-up controller. The wake-up controller is the block with highest priority in terms of power management. It is always powered and waits for a wake-up event from different sources. For lowest power consumption the wake-up controller is clocked by the 4kHz oscillator. If a wake-up event happens and the event is not masked then the wake-up controller powers on the system controller which takes over device control. Before code execution starts the CPU runs a firmware boot sequence and all registers are initialized with their wake-up values. In the case of normal mode the time from wake-up event occurrence until start of application code execution is in the range of several milliseconds. The implemented wake-up sources are:

- Period Wakeup timer (PWDT)

- LF-Receiver: carrier detector

- LF-Receiver: wakeup ID matching circuit

- General purpose I/O (GPIO0~ GPIO5 configurable)

- TMAX detector when device is in Thermal shutdown

The second main function of the wake-up controller is reset handling. The reset signals are generated in the block “power supply and reset generator”. A system-reset may be triggered by:

- Brown out (internal regulated voltage drops below a certain threshold)

- Power on

- Software

- Period wakeup timer underflow

When Power on reset or Brown out reset occurs, all logic will be reset. After reset release, the chip work mode will be decided by the value of GPIO0 and GPIO1(see [Chapter 4.1](#)). Period wakeup timer reset and software reset will not change chip work mode selection.

Furthermore, the wake-up controller comprises the LF ON-OFF timer that allows operating the LF-receiver with a configurable duty cycle for power saving reasons.

### 5.2.1 Period wakeup Timer (PWDT)

The PWDT is a 16-bit timer (SFRs PWDT\_H and PWDT\_L). The main function is to periodically wake-up the device from power down. The timer is active in any low power state and is clocked by the 4kHz oscillator divided by 8 or 512 (SFR bit PMU\_PWDTH\_SEL). The PWDT is counting down, a wake-up event is triggered upon timer underflow. The PWDT should be properly configured to avoid interrupting the telegram transmission or the data acquisition.

Note that the PWDT is set to 0xFFFF after underflow.

The associated registers are:

- PWDT\_H, PWDT\_L: PWDT counter

- TCONL.PMU\_PWDTH\_SEL: Setting this bit selects the PWDT clock division value

### 5.2.2 LF ON-OFF Timer

The ON-OFF timer is used for switching the LF receiver on and off with a low duty cycle in order to save energy. The ON-timer is an 8-bit timer, and the OFF-timer is a 12-bit timer. Both the ON-timer and OFF-timer are clocked by 4kHz oscillator. Consequently, the timer supports long OFF-times of up to 4 seconds and shorter ON-times of maximal 0.256 second.

The user does not need to directly access the ON-OFF timer registers since the firmware function LIB\_LF\_LP\_ONOFF\_CFG() can be used for configuration. Setting bits LF\_LP\_MODE and LF\_WAKE\_EN activates the ON-OFF timer. The current count value of the ON-OFF timer cannot be read by software.

Associated registers:

- PCON, bits LF\_WAKE\_EN

- LF\_LP\_CFG0, bits LF\_LP\_MODE

### 5.2.3 LF Receiver Wake-up/Resume Events

The LF receiver wake-up events are:

- Carrier detected

- Wake-up pattern match

### 5.2.4 General Purpose I/O Wake-up/Resume Event

All I/O Ports (GPIO0~GPIO5) can be configured as an external wake-up source. In order to use this wake-up source, the corresponding GPIO needs to be configured as input (SFR bits GPIO0DIR~GPIO5DIR=1), the corresponding pull resistor must be enabled (SFR bits GPIO0\_PUPD~GPIO5\_PUPD=0) and the corresponding wake-up must be enabled (SFR bits IO0\_WAKE\_FLAG\_EN=1 and IO1\_WAKE\_FLAG\_EN=1) and the corresponding wake-up I/O must be selected(WAKE\_IO\_SEL[1:0]).

**Note:** Note that the General purpose I/O wake-up is triggered on low level only.

**Table 5-1 Truth Table of Wake-Up I/O Selection**

| GPIOOnDIR | GPIOOn_PUPD | GPIOOnOUT | IO0_WAKE_FLAG_EN<br>(GPIODIR[7]) | IO1_WAKE_FLAG_EN<br>(GPIODIR[6]) | WAKE_IO_SEL[1:0]<br>(GPIODATN[7:6]) | Selected wake-up I/O    |

|-----------|-------------|-----------|----------------------------------|----------------------------------|-------------------------------------|-------------------------|

| 1         | 0           | 1         | 0                                | 0                                | Ignore                              | Disable                 |

| 1         | 0           | 1         | 0                                | 1                                | 00                                  | GPIO2                   |

| 1         | 0           | 1         | 0                                | 1                                | 01                                  | GPIO3                   |

| 1         | 0           | 1         | 0                                | 1                                | 10                                  | GPIO5                   |

| 1         | 0           | 1         | 0                                | 1                                | 11                                  | GPIO2<br>GPIO3<br>GPIO5 |

| 1         | 0           | 1         | 1                                | 0                                | 00                                  | GPIO0                   |

| 1         | 0           | 1         | 1                                | 0                                | 01                                  | GPIO1                   |

| 1         | 0           | 1         | 1                                | 0                                | 10                                  | GPIO4                   |

| 1         | 0           | 1         | 1                                | 0                                | 11                                  | GPIO0<br>GPIO1<br>GPIO5 |

| 1         | 0           | 1         | 1                                | 1                                | 00                                  | GPIO0<br>GPIO2          |

| 1         | 0           | 1         | 1                                | 1                                | 01                                  | GPIO1<br>GPIO3          |

| 1         | 0           | 1         | 1                                | 1                                | 10                                  | GPIO4<br>GPIO5          |

| 1         | 0           | 1         | 1                                | 1                                | 11                                  | GPIO0~<br>GPIO5         |

Associated registers:

- GPIODIR, GPIO input or output selection

- GPIOPUPD, GPIO wake-up enable and pullup/pulldown selection

- GPIODATN, bits WAKE\_IO\_SEL[1:0], Wake-up I/O selection

### 5.2.5 Power-On and Under-Voltage Reset

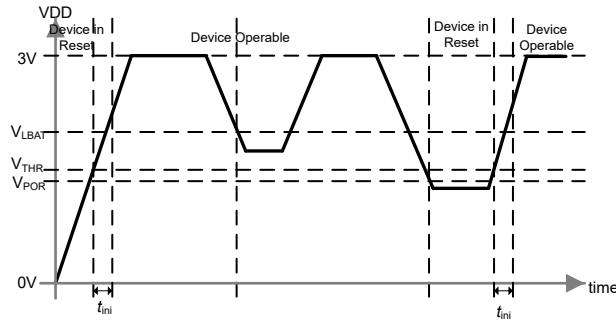

Figure 5-2 shows the device behavior depending on voltage at VDD pin. If the voltage falls below a certain threshold  $V_{POR}$  a system-reset is triggered. The device stays in reset until the voltage at VDD pin exceeds the reset release threshold  $V_{THR}$ . After reset release the device initialization is started which takes a certain time,  $t_{ini}$ . After the initialization phase the operation mode of the device can be selected by strapping the GPIO0 and GPIO1.

Figure 5-2 Power-On and Under-Voltage Reset Behavior

### 5.2.6 Software Reset

After a reset triggered by software the device runs through the reset boot sequence. The software reset can be triggered by setting the bit RESET (located in register EPCON) in application code. Software reset mainly focus on reset in Normal mode or Debug mode, and it will reset Core and System Controller block, and the chip mode selection is not affected.

Associated registers:

- EPCON(bit RESET for triggering software reset)

### 5.2.7 Thermal Shutdown

Thermal shutdown function is enabled by setting the bit TSHDWN\_EN (located in register PCON) in application code, and the TMAX detector is active when TSHDWN\_EN=1. A flag TGOOD (location in register EPCON) is keep high level if the temperature is below the hot temperature threshold Thot\_th. If the temperature is above hot temperature threshold Thot\_th, the flag TGOOD is pulled down by TMAX detector, so the application code can polling the flag TGOOD, then enter Thermal shutdown by setting the bit PDWN(location in register PCON). Once in Thermal shutdown the device is only release if the on-chip TMAX detector indicates a temperature below the hot release temperature Thot\_re. After release from Thermal shutdown a wake-up is performed.

Associated registers:

- EPCON (bit TGOOD for indicating TMAX detector)

- PCON (bit TSHDWN\_EN for enable TMAX detector, bit PDWN for enter Thermal shutdown)

## 5.3 System Controller

Main function of the system controller is power management after device wake-up from power-down or device resume from CPU idle. Unlike the wake-up controller most other circuits can be disconnected from power individually. Depending on the device state the system controller connects the required blocks to the power domain. Here the device states are listed, ordered by current consumption, starting with the state with highest current consumption:

- Run state

- CPU idle state (Run state with CPU disconnected from system clock)

- Powerdown state (optional with LF receiver enabled)

### 5.3.1 Measurement Controller

Refer to the associated firmware function:

- LIB\_MEAS\_PRESSURE()

- LIB\_MEAS\_TEMPERATURE()

- LIB\_MEAS\_VOLTAGE()

- LIB\_MEAS\_ACCEL()

### 5.3.2 WAM Controller

Refer to the associated firmware function:

- WamB\_Init()

- WamB\_On()

- WamB\_Off()

- WamB\_GetFiltCycle()

## 5.4 Clock Generators

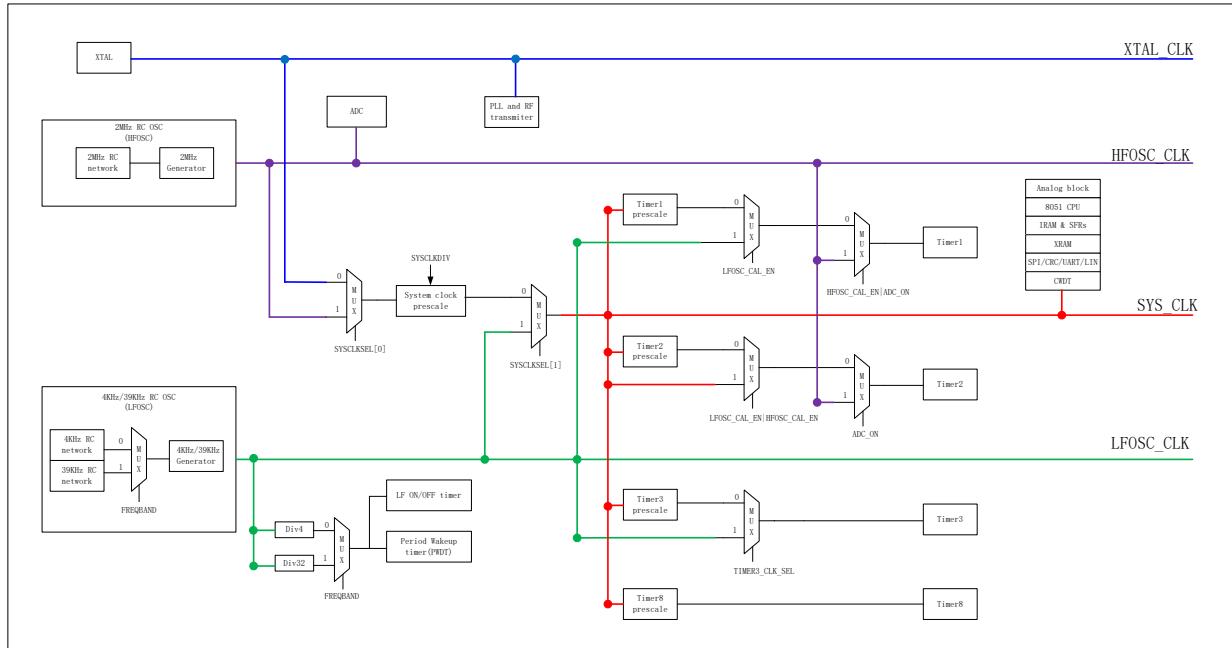

The SNP73X comprises three on-chip RC oscillators in order to fulfill the extremely different requirements in terms of power consumption and cycle time for different operating states. A 4kHz oscillator is operated in power-down for lowest power consumption. A 39kHz oscillator is implemented for clocking the system controller and the digital part of the LF receiver. Finally, a 2MHz oscillator is mainly used for the ADC. The 2MHz clock may be divided (controlled by bit field SYSCLKDIV). The 39kHz oscillator is trimmed in production. However, the user can use the associated firmware function to calibration all the three on-chip RC oscillators if needed.

All the three on-chip RC oscillators can be configured as system clock for CPU (controlled by bit field SYSCLKSEL).

**! Attention:** Note that the 4kHz and 39kHz oscillator cannot be enabled simultaneously.

For RF transmission and calibration purposes a crystal oscillator (XTAL) is implemented as well. The XTAL can also be used as system clock by configuring the SFR bits SYSCLKSEL and can be divided by configuring the SFR bits SYSCLKDIV.

**Figure 5-3 Clock distribution diagram.**

Associated registers:

- SYSCLKSEL (system clock selection)

- SYSCLKDIV (XTAL or RC OSC 2MHz clock division)

Associated registers:

- LIB\_HF\_CLK\_CAL()

- LIB\_PD\_CLK\_CAL()

- LIB\_LF\_CLK\_CAL()

- LIB\_SYSCLK\_SEL()

- LIB\_HFOSC\_START()

- LIB\_HFOSC\_STOP()

- LIB\_XTAL\_OSC\_START()

- LIB\_XTAL\_OSC\_STOP()

## 5.5 Core

The Core comprises an 1T cycle 8051 based MCU and the following peripherals:

- Timer Module

- Hardware CRC

- Core watchdog timer (CWDT)

- Multiplication-Division Unit (MDU)

- UART/LIN interface

- SPI interface

### 5.5.1 Timer Module

There are 4 general purpose counters with 16 bits, Timer1/Timer2/Timer3/Timer8.

- **Timer1**

This timer is a 16 bits counter. It counts down from the value previously loaded into the counter and stops when it reaches zero. The counter will not wrap around, so a new value must be written into T1L and T1H to start a new period count, and these values will be loaded on timer1 enable.

- **Timer2**

This timer is a 16 bits counter which can count-down or count-up. The following list is its work mode:

1. **mode 0:** 16 bits decrease counter. In this mode, source clock is decided by SFR TCONL configure (system clock divided by 16 or 128). If the counter reaches zero, an all-zero detect will trigger on the next falling edge of the clock (which will stop the clock in the clock block).

2. **mode 1:** used as ADC data accumulator. During ADC working on, please not take timer2 as other normal usage.

3. **mode 2:** used as pseudo-random generator.

4. **mode 3:** 16 bits increment counter. In this mode source clock is decided by SFR TCONL configure. When RC OSC 4kHz/39kHz calibration bit (TCONL[4]) or RC OSC 2MHz calibration bit is set (TCONL[3]) is set then the source clock will switch to XTAL by hardware automatically. All-zero detect is disabled in this mode but the counter will stop when Timer1 reaches zero (this operation is crucial for the correct calibration of the 4kHz/39kHz and 2MHz clock). In certain situations, the interrupt from Timer1 should also stop the clock of Timer2.

- **Timer3**

This is a 16 bits counter that can be used as a down counter.

When Timer3 is used as 16-bit down counter, the source clock is decided by SFR bit FAST\_T3, and if the counter reaches zero, SFR bit T3\_FULL will be set by hardware. In order to clear this interrupt, T3\_ON should be off.

**Note:** Note that the timer3 is used as baud-rate generator for UART transmission when UART is enabled.

- **Timer8**

This timer is a 16 bits counter which supports input capture, output compare and the generation of PWM. The main function of timer8 is as follows:

- Configurable up or up-down counter with initial and final value.

- Configurable input capture on rising edges, falling edges or both edges.

- Configurable output compare mode the output signal be set, cleared or toggled on match.

- Configurable PWM for center-aligned PWM or edge-aligned PWM with deadtime insertion.

Associated registers for timer1/2/3:

- TCONH, TCONL

- TH1, TL1

- TH2, TL2

- TH3, TL3

- INTL (timer1/2/3 interrupt flag)

### 5.5.2 Hardware CRC

This module is a generic re-configurable CRC calculator for calculating the CRC of a variable length data sequence. The CRC order (up to 16), polynomial and initial value can be configured by the application.

The CRC is calculated on 8/16 bits basis, therefore the application must break up a long message into individual words and feed these to the calculator sequentially. The intermediate CRC value can be read from SFR CRCH/CRCL after each data input done.

- **CRC function:**

- **STEP1:** initial CRC setting.

Write 0x0000 to the CRC Generator Polynomial register (CRCPOLYH, CRCPOLYL)

Write 0x000F to the CRC Configuration register (CRCCON)

Write the initial CRC value to the CRC register (CRCH, CRCL)

Write polynomial to SFR CRCPOLYH, CRCPOLYL.

- **STEP2:**

Configure the module by writing the CRC order (eg. CRC16) and the message remainder fields of the CRC configuration register (CRCCON).

- **STEP3:**

Write the message to SFR CRCH/CRCL in sequence (MSB first).

Must send CRCH then CRCL.

- **STEP4:**

Update the CRC message remainder field of the SFR CRCCON with the remaining number of bits to process. Write the last message word to the CRC register.

- **STEP5:**

Read the final computed CRC value from the CRC register (CRCH, CRCL).

With hardware CRC associated registers:

- CRCPOLYL

- CRCPOLYH

- CRCCON

- CRCL

- CRCH

### 5.5.3 Core watchdog timer (CWDT)

A count down core watchdog timer (CWDT) using the free running clock offers configurable and robust protection against application lock-up.

The CWDT will generate a system reset when the firmware runs in abnormal loops, the Program Counter will be reset to 0x0000. In order to prevent the reset from CWDT, the firmware should reset the CWDT timer periodically.

**Table 5-2 CWDT period config**

| CWDT_CLK_SEL | CWDT_OV_SLE[2:0] |   |   | Clock source | Overflow time        |

|--------------|------------------|---|---|--------------|----------------------|

| 0            | 0                | 0 | 0 | LFRC         | $2^{5} * T(4kHz)$    |

| 0            | 0                | 0 | 1 | LFRC         | $2^{6} * T(4kHz)$    |

| 0            | 0                | 1 | 0 | LFRC         | $2^{7} * T(4kHz)$    |

| 0            | 0                | 1 | 1 | LFRC         | $2^{8} * T(4kHz)$    |

| 0            | 1                | 0 | 0 | LFRC         | $2^{9} * T(4kHz)$    |

| 0            | 1                | 0 | 1 | LFRC         | $2^{10} * T(4kHz)$   |

| 0            | 1                | 1 | 0 | LFRC         | $2^{11} * T(4kHz)$   |

| 0            | 1                | 1 | 1 | LFRC         | $2^{12} * T(4kHz)$   |

| 1            | 0                | 0 | 0 | System clock | $2^{13} * T(sysclk)$ |

| 1            | 0                | 0 | 1 | System clock | $2^{14} * T(sysclk)$ |

| 1            | 0                | 1 | 0 | System clock | $2^{15} * T(sysclk)$ |

| 1            | 0                | 1 | 1 | System clock | $2^{16} * T(sysclk)$ |

| 1            | 1                | 0 | 0 | System clock | $2^{17} * T(sysclk)$ |

| 1            | 1                | 0 | 1 | System clock | $2^{18} * T(sysclk)$ |

| 1            | 1                | 1 | 0 | System clock | $2^{19} * T(sysclk)$ |

| 1            | 1                | 1 | 1 | System clock | $2^{20} * T(sysclk)$ |

Associated registers:

- TCONH (bits CWDT\_EN, CWDT\_CLK\_SEL, CWDT\_OV\_SEL)

- EPCON (bit CWDT\_RST)

### 5.5.4 Multiplication-Division Unit (MDU)

The MDU provides 32-bit division, 16-bit multiplication, shift and normalize operations. All operations are unsigned integer operations.

Refer to “SNP739D0X\_Reference\_Manual” for MDU details usage.

### 5.5.5 I2C Controller

The SNP739D features a slave hardware I2C interface with the fixed device address 0x6C. When the I2C is activated, pin GPIO0 is configured as input and serves as clock line (SCL). Pin GPIO1 is initialized as input, too, and serves as data line (SDA). Both lines need a pull-up resistor, either an external resistor or by activating the internal pullup resistors. The active device transmits data by pulling the data line low.

In program-mode and debug-mode the I2C interface is managed by an I2C firmware . Only certain I2C commands are available in these modes, no application code can be executed. The internal pull-up resistors are enabled by the I2C handler.

In normal mode the I2C (if needed) must be managed by application code. For activating the I2C interface the bit I2CEN must be set. The internal pull-up resistors are automatically set for GPIO0 and GPIO1. The port direction register is managed automatically by the I2C interface.

#### Receiving data from master in normal mode

Once activated, the I2C register waits for a start condition. The following 8 bits are interpreted as device address and compared to 0x6C. If the received address matches, acknowledge (ACK) is generated, i.e. the data line is pulled down on the 9th clock pulse. The next 8 bits are interpreted as data bits and are also acknowledged by pulling the data line low. The complete reception of a data byte is indicated by the flag RXRDY. The application code needs to poll this flag and fetch the data from the register I2CD. RXRDY must be cleared by firmware write 0 to it. This procedure is repeated for incoming data bytes until a stop condition is received. If the I2C event interrupt is enabled, the receiver raises an interrupt on every received byte from the I2C bus.

#### Transmitting data from SNP739D to master in normal mode

The LSB of the device address serves as a read-write indicator. Thus, in order to put the SNP739D in data transmission mode, the master must send the device address 0x6D.

A transmit data buffer is used for I2C transmitting data, and it only supports the transmission of two bytes messages from the chip. The TXRESET status bit must be cleared for the transmit data buffer and the two bytes data that make up the message should then be written into the buffer by the firmware. When a two-byte data has been transmitted, the TXDONE bit is set. If the I2C event interrupt is enabled, the TXDONE interrupt will only be raised for a two (or more) bytes read and once raised will not occur again until the status bit TXRESET has been cleared by the firmware.

**Note:** Note that the system clock should be at least 2 times faster than I2C master clock.

Associated registers:

- I2CS

- I2CD

- I2CEN

### 5.5.6 UART/LIN Interface

The SNP739D has a hardware UART/LIN interface. If enabled, pin GPIO3 serves as UART-TX and GPIO4 as UART-RX. The device embeds two universal synchronous/asynchronous receivers /transmitters which communicate at speeds of up to 2 Mbit/s.

**Table 5-3 UART mode selection**

| MSEL0 | MSEL1 | Mode   | Description    | Baud rate     |

|-------|-------|--------|----------------|---------------|

| 0     | 0     | Mode 0 | Shift register | SYSCLK/12     |

| 0     | 1     | Mode 1 | 8-bit UART     | Variable      |

| 1     | 0     | Mode 2 | 9-bit UART     | Variable      |

| 1     | 1     | Mode 3 | 9-bit UART     | Same as Mode2 |

$$BaudRate = \frac{f_{SYS\_clk}}{T3L + 1}$$

In mode 0 the Serial Port 0 operates as synchronous transmitter/receiver.8 bits are transmitted with LSB first. The baud rate is fixed at 1/12 of the main clock frequency. Transmission is started by writing data to UARTBUF register.

In mode 1 the UART operates as asynchronous transmitter/receiver with 8 data bits and programmable baud rate.